AI算力之争,太空领域进展到哪了?

AI时代的芯片算力之争,地面,其它芯片争霸;太空,高性能SRAMFPGA做主!FPGA强大的可重构能力,能够在高性能和高可靠之间无缝切换,这是其无可比拟的独特优势,本身就意味著低成本、大节省,在商业航天时代具有爆发式应用前景。

冷战时期美苏争霸的星球大战,余温尚在,现在以AI为制胜战略高点的大国芯片算力之争,帷幕拉开。

AI时代的算力成本决定了创新成本。

算力源于芯片,作为算法和数据的基础设施,其性能直接决定了AI产业的发展。

2018年,当微软公司使用25万片FPGA,构造当时世界上最大的AI计算机脑波,据称性能表现超过谷歌研发的专有ASIC,即TPU芯片。

因人机围棋大战出圈的AlphaGo,背后隐藏的AI训练功臣。

Microsoft’s Project Brainwave claims win over Google TPU

同在2018年,美国由NASA牵头,启动了太空高性能计算项目HPSC(High Performance Spaceflight Computing),目标是把空间处理器的计算能力,提升2个数量级以上。

定位为改变未来游戏规则的重要组成。

2024年,杭州的之江实验室提出打造三体计算星座,把算力送上太空,应对在轨卫星数量快速增长带来的算力挑战。

打造一个千星规模的天基智能计算基础设施,建成后总算力可达1000P。

而拥有全球最大的亚米级商业遥感卫星星座的长光卫星,按其科创板IPO申报稿披露:“目前拥有72颗卫星星座,累积存档的数据库遥感数据总量,是13PB。”

商业航天的兴起,把计算与太空再次紧密链接在一起,也将计算卫星推上前台。

使之成为继通信、导航、遥感卫星的第四类“专用”卫星。

作为“Star Compute-星算计划”的合作方,按照商业航天明星初创,国星宇航在其公众号的消息,与软通动力和之江实验室,共同开启太空计算新时代。

端侧高效能计算的神龙教主

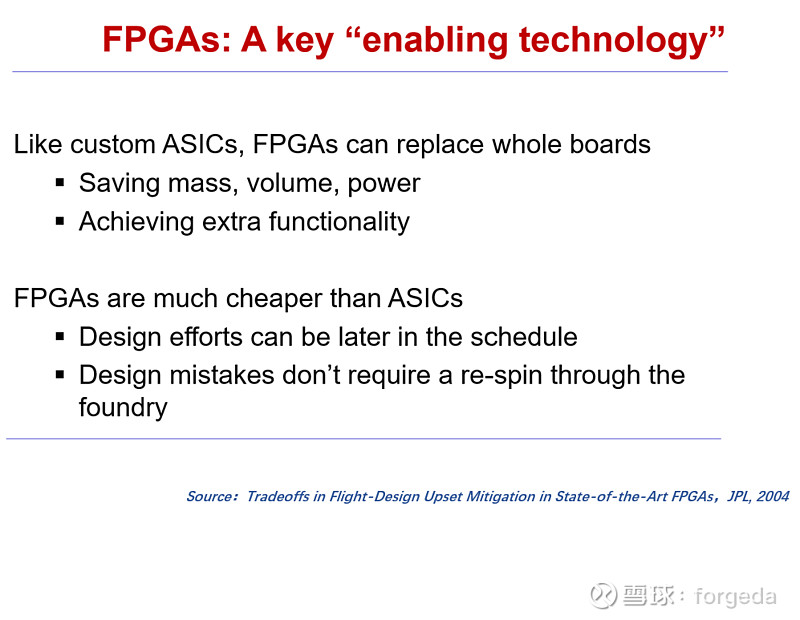

如果说在地面的数据中心AI训练,现在是GPU为王,已经成就英伟达霸业的话,那么在空间为代表的端侧数据处理,则是FPGA做主,一直延续到现在的AI时代。

首次在空间领域应用,最早可溯源三十前的1993年。

最先进入航天工程人员视野的,是原Actel公司的高可靠反熔丝芯片Anti-fuse FPGA。到1997年时,已成为火星探测器探路者号(PathFinder)的主要组成单元。

到2004年时,赛灵思的高性能SRAM FPGA在空间领域得到认可,逐步站稳脚跟。现在的空间应用市场份额稳居行业第二,仅屈居收购了Microsemi公司的微芯科技之后。

从作为几代火星车的关键组件使用,到扮演在轨数据的主处理器角色。包括2008年后以SpaceCube为代表的高性能计算,以及现在以Startlink为标杆的低轨卫星数据处理平台。

火星车项目作为SRAM FPGA在航天领域开山之作,也是最著名的应用案例之一,自然出现在赛灵思为庆祝公司为成立25周年时特别出版的专刊。

当期所选二十个最具代表性的客户创新案例,航天领域就占有三席。

在提升在轨处理能力方面,独树一帜。

作为价格亲民的“ASIC”,还支持进行在轨错误修复,甚至功能升级。

现在已经是空间飞行器的关键使能技术,不可或缺。

AI时代的创新成本,在很大程度上由芯片算力成本直接决定。

对于太空应用场景,与地面数据中心可以大规模集群堆算力的使用方式,并不适用。

液冷散热等技术,更是天方夜谭,水中捞月。

空间领域高温差高辐射环境下,只能使用非常有限的电力,完成遥感、通信、数据加工等复杂的计算任务。权衡评估整个系统的PPA要求,更为严苛。

除了综合考虑面积(Size)、重量(Weight)、功耗(Power)和成本(Cost)的SWaP-C指标,现在更是额外增加了为应对数据爆炸的高性能计算需求。

这也使开发抗辐射(Radiation-Hardened)飞行处理器CPU芯片,在制造工艺上做特殊处理的传统路线,以最大化满足可靠和安全作为绝对优先,一招鲜,不再是可以吃遍天。

至少不再像以前那样“有效”。

而这正是高性能FPGA的绝佳机会。

特别是高性能SRAM FPGA,回顾其在航天领域的应用发展,从火星车项目开始起步,在过去的30年间大致经历了三个关键节点:

1993年-2004年,大胆设想,小心求证阶段;

2008年-2018年,空间高性能计算平台诞生;

现在的异构计算时代,太空人工智能来临。

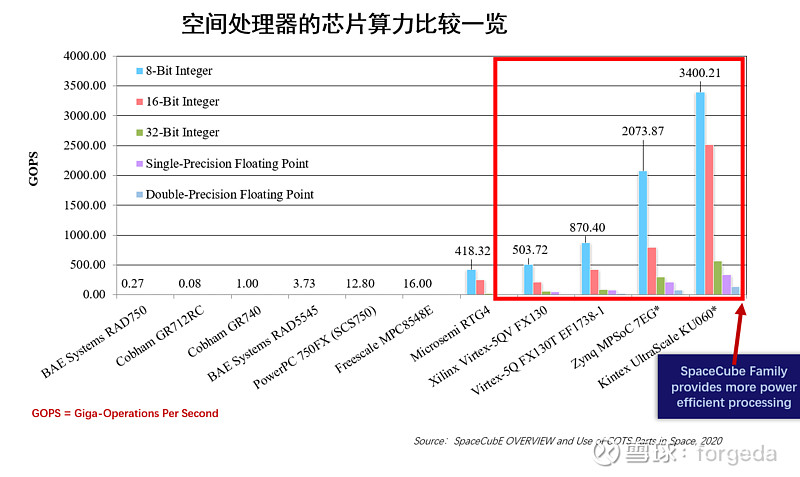

截至目前,在空间使用的处理器算力比较中,FPGA芯片表现优异,说是一枝独秀也不为过。

以至于做抗辐CPU,采用Sparc架构的创业板上市公司航宇微(300053.SZ),当年欧比特在业绩下滑的解释性公告中,FPGA冲得太猛,也是原因之一。

微芯科技在器件级别(Hardened By Device)的抗辐射FPGA芯片RTG4,已经是传统抗辐CPU的1个数量级以上。

AMD的耐辐射(Radiation-Tolerant)技术,需要用户在设计时加固(Design-Level Hardening)的SRAM FPGA芯片,又是前者的数十倍。

并且可预期的性能优势领先优势,还将进一步持续快速拉大。

AMD2024Q3季报电话会议显示,在上季度完成了其第二代Versal系列首款产品,Telluride的流片。算力与目前最先进的VC1902相比,又有10倍提升,并且能够在单芯片上直接加速AI应用。

现在进入到航天和防务部门的耐辐射VC1902,对应的峰值性能为133 TOPS,比现在采用20nm工艺的抗辐旗舰芯片Kintex UltraScale060相比,已经提升40倍。

早先年代的芯片,也可以说是为航天事业服务才产生的。

空间应用市场,曾是芯片最早最重要的领域。

在上世纪六十年代开始,以1961年美国的阿波罗登月计划为例,仅是NASA一家机构,就几乎承包了那个年代60%以上的芯片订单。

当一台有着16536个晶体管的先进计算机已经被带上太空时,地面上的处理器仅有2300个晶体管。

第一台基于硅集成电路的计算机阿波罗制导计算机,能够自行处理复杂的轨迹方程,并在飞行过程中实时发出制导指令。在该装置的整个研发过程中,按照EDA巨头新思科技的统计数据,仅MIT一家单位,就消耗了当时全世界60%的可用集成电路。

但半导体技术的发展,已今非昔比。

无论是芯片制程工艺,特别是计算性能上,太空与地面相比,至少落后两代以上。

比如下一代空间设备,传感器将以超高采样率工作,与以前相比,所产生的巨量数据规模,远超现有使用的芯片计算能力。

2009年,戈达德飞控中心GSFC研发的空间高性能计算机(SpaceCube),使用赛灵思普通商用级FPGA芯片(Virtex-4 FX60),提供关键交汇对接信号完成哈勃望远镜的维修任务。

采用异构处理方法,融合抗辐器件以及商用FPGA模块,同时以一种创新的架构,最大程度利用芯片内部CPU、DSP和LUT的处理能力。

SpaceCube研发团队的目标是,在轨处理能力提升一个数量级以上,更好满足下一代空间任务的需求。

辐射引起的“小问题”可能偶尔会发生,只要恰当处理就行……通过巧妙的系统设计,可以实现任何级别的高可靠!

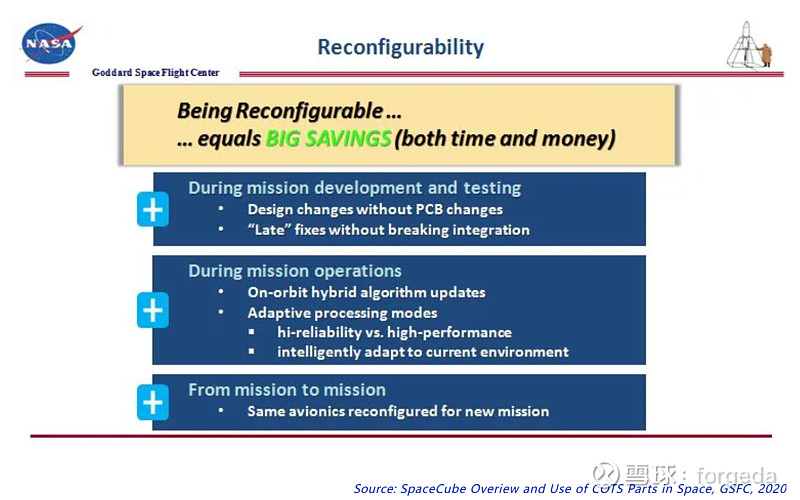

借用戈达飞控中心嵌入式部门(Embedded Processing Group)2020年所说的,FPGA可重构计算能力,本身就意味着低成本大节省。

在NASA的诸多下属机构中,戈达飞控(GSFC)远没有专接大项目、大合同的JPL那样名声显赫。其任务多集中在航天器的在轨运维、燃料加注等“非核心”任务,与"卫星测控中心"较为类似。

SpaceCube项目启动伊始,经费预算有限,时间有限,如果按照NASA一直以来的防护设计思路,将成为不可能完成的任务。

有点被迫向市场找饭吃的意思。

在获得NASA技术创新大奖之后,其负责人Tom Flatley接受“技术简报”访谈时的原话:

“我们是在类似洛克希德-马丁(LMT)“臭鼬工厂“的创新环境下,实现同一类设计方法和策略。就像我们对于更大的系统所做的那样,只是没有那些大型卫星中的管理流程开销。”

本质上的挑战,在于芯片选型和设计过程。

“找到一个中间地带,利用地面商用处理的高端处理能力,使其在空间环境下,能够可靠执行科学数据处理任务。”

获得可接受的可靠性和安全性。

对于科学数据处理,如果每隔一段时间出现一个坏的像素点,或者你必须重新进行复位重启,当然也能接受,只要能够获得100倍以上的能力提升。

以前是不计成本保可靠性,可以花长时间精心打磨产品,现在则是低成本、批量化、快速生产部署。

低成本设计理念一直在延续,在商业航天时代即将结出硕果。

大力出奇迹的EDA硬件辅助验证工具

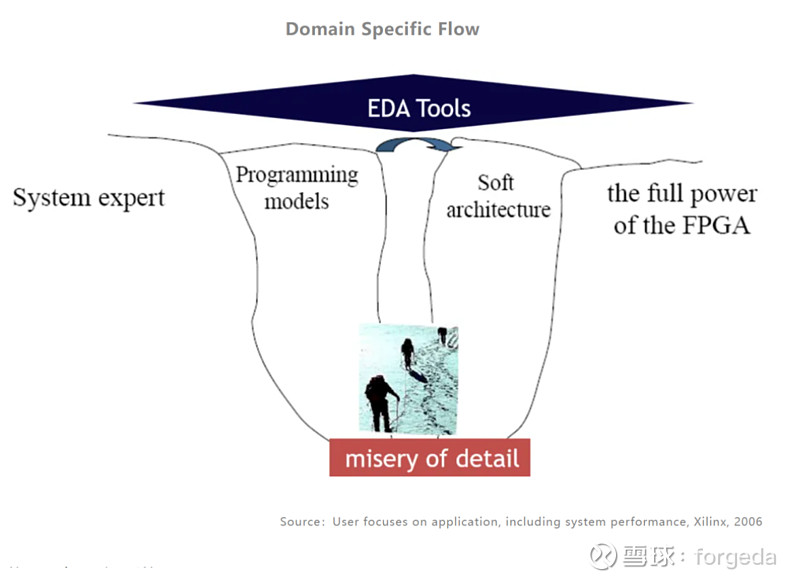

FPGA的强大,不仅取决于芯片本身,也与EDA工具使用密不可分。

在空间应用市场,更是FPGA在重大航天工程屡立战功的幕后英雄。

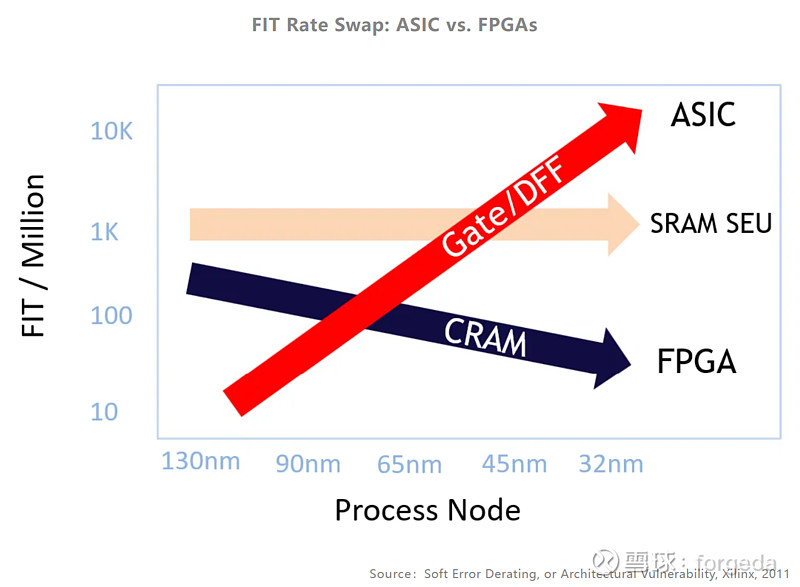

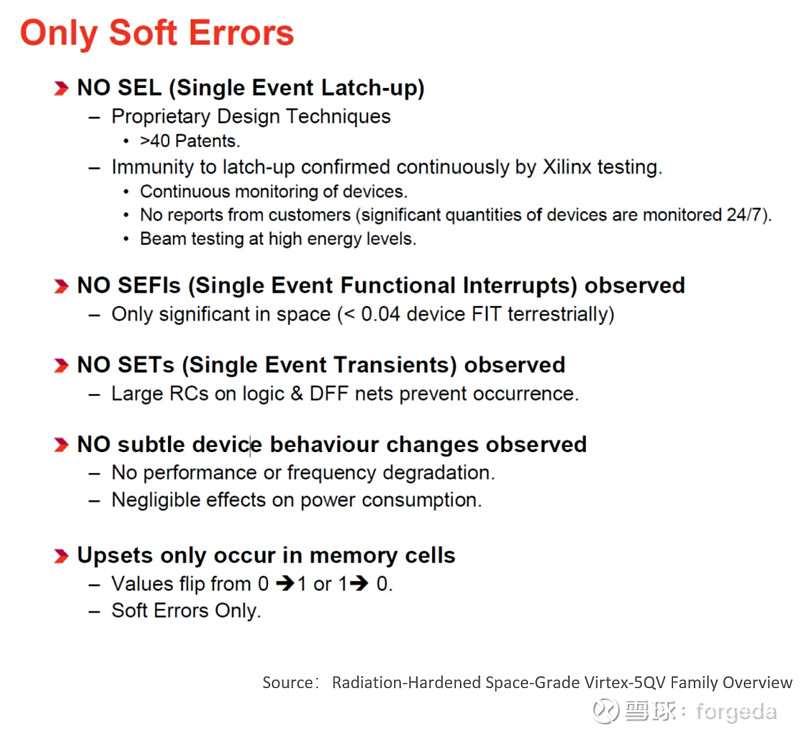

芯片是信息系统的基石,所有的数字芯片,都会存在软错误或软失效。

虽然会导致硬件电路出现功能故障,但如果“重启”,系统将恢复正常运行。这种短暂的、瞬时的功能故障,通常称之为软错误。

对于ASIC芯片,主要是门级电路(Gates)、寄存器(DFF)中01数值的翻转,由单粒子效应引发的瞬态故障(SET)。

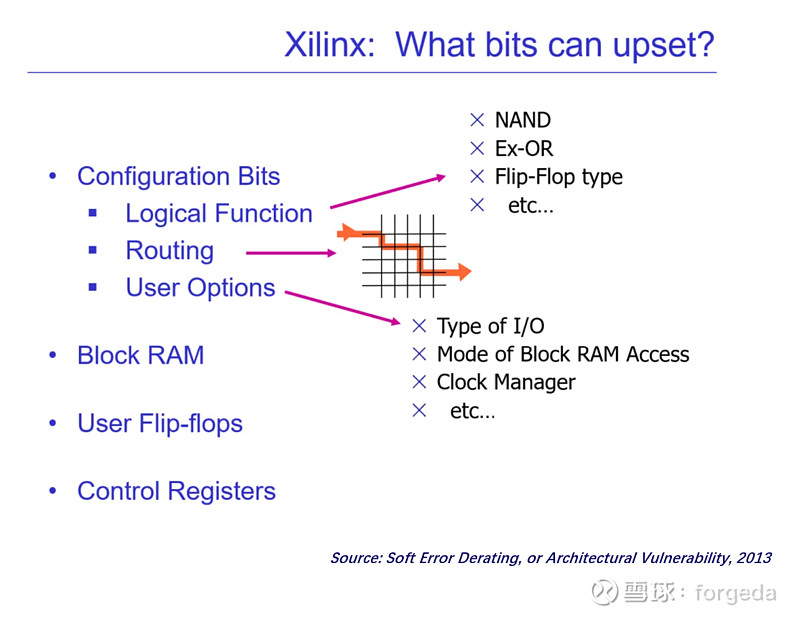

对于高性能FPGA,还需要特别关注其配置存储器(CRAM)中01数据,受单粒子效应影响被动发生改变,可能引发的系统异常问题。

这也是“SEU免疫型”竞品,常用来“攻击”的靶点。

在任务关键、安全关键的行业使用时,通常采取额外三模冗余设计、锁步技术等软错误缓解策略在内的额外“加固设计”措施。

在航天领域,即便用户使用的最高等级QR型芯片,也必须考虑软错误问题。

既包括SRAM FPGA芯片特有、用于直接配置硬件电路CRAM数据,也包含像ASIC一样的门级电路和寄存器(Gates/DFF)。后者只能在源码和网表级进行仿真验证,如新思科技的Synplify Premier等工具。

运行速度慢,可能是唯一的“美中不足”。

对芯片内部的状态机(FSM)、关键寄存器(Key Register)的测试验证,很难做到100%的代码全覆盖。

赛灵思推出初代Virtex芯片的同一年,就联合JPL实验室成立单粒子效应联盟(Single-Event Effects Consortium, SEEC),2000年,将其进一步正式升级为的商业化组织。

Xilinx Radiation Test Consortium (XRTC)

共同研发大型专用测试设备XRTC,并且只面向境内联盟成员开放使用。

设备共有两大核心组件:

对FPGA进行位流故障注入的回归测试模块,服务日常优化迭代设计;以及对设计做最终的确认测试,满足行业黄金法则(Golden Rule):破坏性测试的辐照试验。

前者为后一阶段服务,避免因直接进行辐照试验,一旦数据结果不如预期,可能造成巨大的财务风险和时间成本。

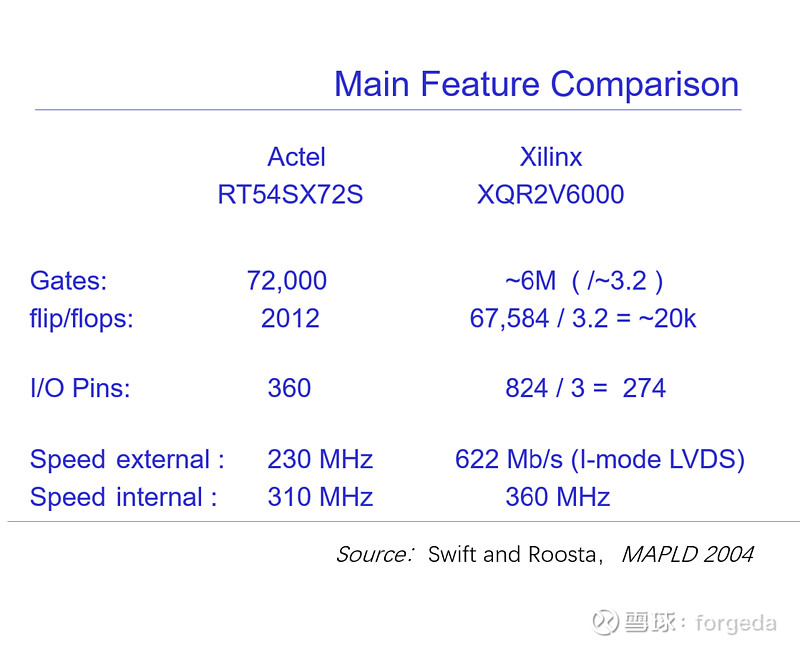

2008年时,NASA的火星探测器平台(MER,Mars Exploration Rovers),使用的高可靠FPGA,硬件规模仅为32K 等效逻辑门;

但即便对于一个典型的FPGA应用设计,验证时间可能也长达3个月。

并且测试用例的开发,与FPGA应用设计可能由同一个团队完成,手工创建的测试用例可能本身就存在问题。

只使用数字仿真方式进行验证,因测试覆盖率难免受限,设计阶段隐藏的bug,将不可避免的逃逸到部署使用阶段。

虽然可以进行在线修复“打补丁”,但肯定会影响任务的“正常执行”。

好奇号火星车的载荷(MSL, Mars Science Laboratory)使用的高性能SRAM FPGA,硬件容量已经达到近200万门,是反熔丝高可靠FPGA的近30倍。

寄存器(flip/flops)数据规模则达到了20K以上,也是后者10倍,相应带来了验证工作量的急剧增加。

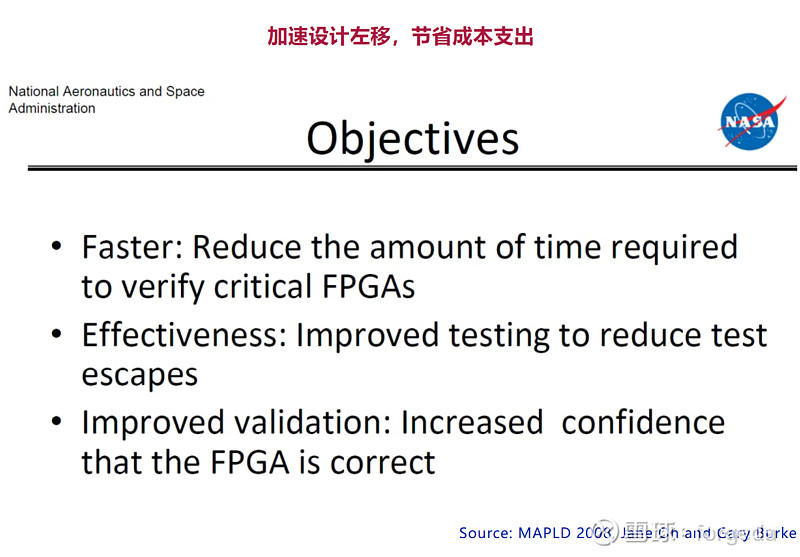

更快,更高效,才能更好确认设计成果。

换而言之,只有创新的EDA工具,才能真正提升设计开发效率。

既然市场上现有的代表FPGA最先进调试验证能力的EDA工具指望不上,那就从实际工程中所感受的“痛点”出发,启动FVAX(FPGA Verification Accelerator)项目。

与服务ASIC流片的EDA硬件辅助验证技术同源,源于赛灵思,又高于赛灵思。

尽管一直走在异构计算,硬件加速的最前沿,但EDA硬件辅助验证的两大行业工具,无论是对SoC设计调试能力最强的硬件仿真平台(Emulation),还是运行速度最快的高性能原型验证系统(Prototyping),主要面向需要流片的IC芯片设计。

服务不差钱的头部用户,以及获得大额融资的少数明星初创公司。

基于成本因素,技术实用性层面等层面考虑,始终与FPGA终端市场距离遥远,EDA供应商向行业应用设计用户,推广使用的动力不足,扩张能力有限。

时至今日,随着FPGA应用设计更趋复杂,系统验证所需的工程量急剧加大。

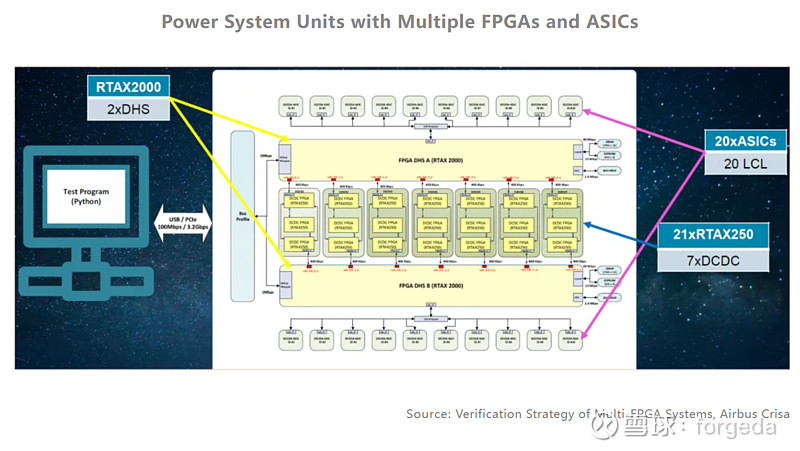

以空客公司航天与防务部门的一套用于电源管理的空间数据处理系统(DHS)为例,包含23块抗辐FPGA,20块抗辐ASIC,一共43块芯片的异构计算系统。

如果只是沿用以往采取的数字仿真验证方式,运行慢且低效率。

"哪怕是只有几个毫秒的处理,在数字仿真器中,也需要花费数分钟,甚至数小时;跑个回归测试,更是需要耗费数天时间"——摘自"终极的复杂,是简单"

欧洲巨头空客,采购了西门子的商用高性能原型验证系统proFPGA,使用一款赛灵思的大容量FPGA,以UV440作为验证平台,就可为整套系统调试验证的提供所需的全部硬件资源。

并且无需设计分割、时分复用等验证超大规模IC设计才会需要的专有技术。

还可保持性能最优,速度最快。

将原本需要运行90个小时的仿真任务,90分钟完成,验证效率提升60倍以上。

在EDA硬件辅助验证行业,如果以已经构建技术和市场双领先优先优势的思尔芯公司作对比,同样是以UV440 FPGA构建的Prodigy芯神瞳,已经是8年前的行业旗舰产品。

与西门子等EDA巨头保持同步。

属于2.5代以前的产品,后续又推出VU19P,VP1902两代,以及在两代旗舰之间的VP1802,则是增加AIE模块。

对于动辄数百亿门的超大规模IC设计,单UV440 FPGA板卡的硬件容量,可能稍显“落伍”,但在FPGA应用市场,还非常富裕。已经足够胜任任何复杂系统的调试验证需求。

作为电子设备中的关键组件,FPGA芯片能够快速定制为用户所需的功能。

空间电子行业正在迅速演进,以满足复杂的全球竞争市场。这样的转变使得空间电子行业与地面防务市场,更为类似。

从大型专用设备,昂贵复杂的硬件平台,向轻量级进化,已经渐成趋势。

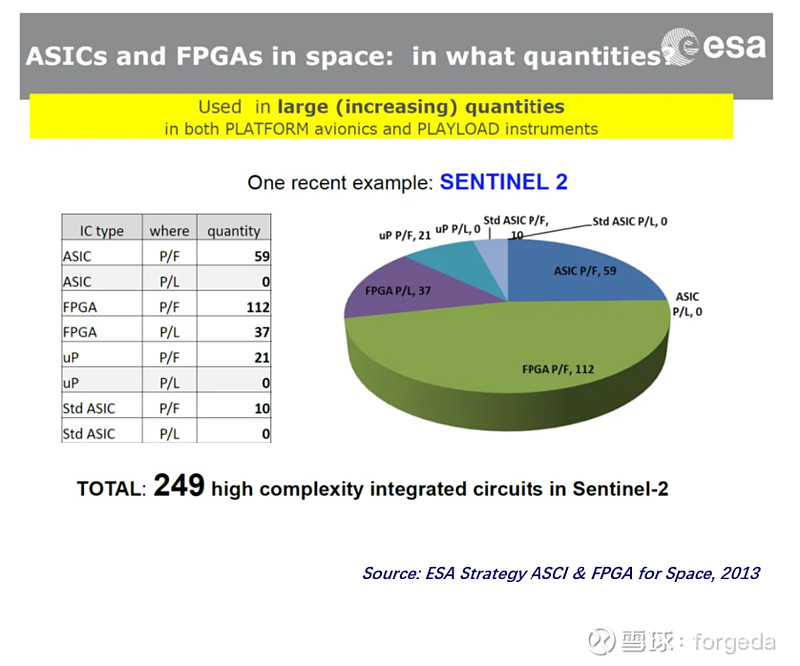

相比ASIC芯片,FPGA在空间电子设备中的占比逐年增加。以欧空局的哨兵2号卫星为例,使用的249个芯片中,就有149片是FPGA,占比超过50%。

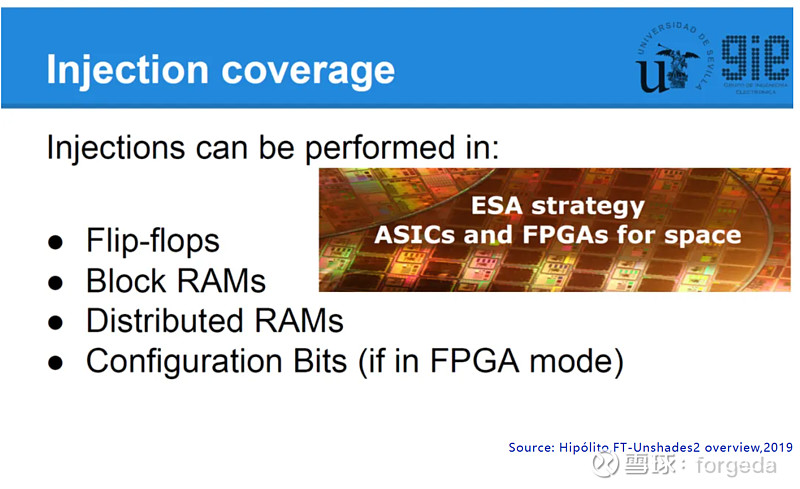

欧空局推荐使用的FT-UNSHADES2,与美国大型专用设备XRTC相比,更进一步,除了更小型轻量之外,还额外扩展了故障注入的位流数据类型。

从最早的仿真加速功能起步,主要服务航天ASIC设计制造的前端验证。

增加FPGA应用开发专用的SEU测试功能,即FPGA模式。

前者是2008年NASA启动的FVAX项目欧洲本地化,后者则是XRTC设备的欧洲平替版。

也可以将其视为EDA硬件辅助验证最早的跨界服务。

FPGA作为价格亲民的ASIC,既是创新,也是应有之义。

不管是新型航天,还是传统航天,正在从以往为小批量应用定制专有ASIC芯片,转向使用商用现货FPGA芯片,同样带来了新的调试验证需求。

商业航天时代的新机遇

航天高端俱乐部,迎来新成员。

按照NASA的观点,在挖掘太空经济金矿的大浪潮中,先进芯片就像是卖铲子的,是否真的能淘到金矿姑且不论,卖挖矿工具可以先把钱挣了。

In the gold rush of space exploration,chip technology has provided a better shovel.

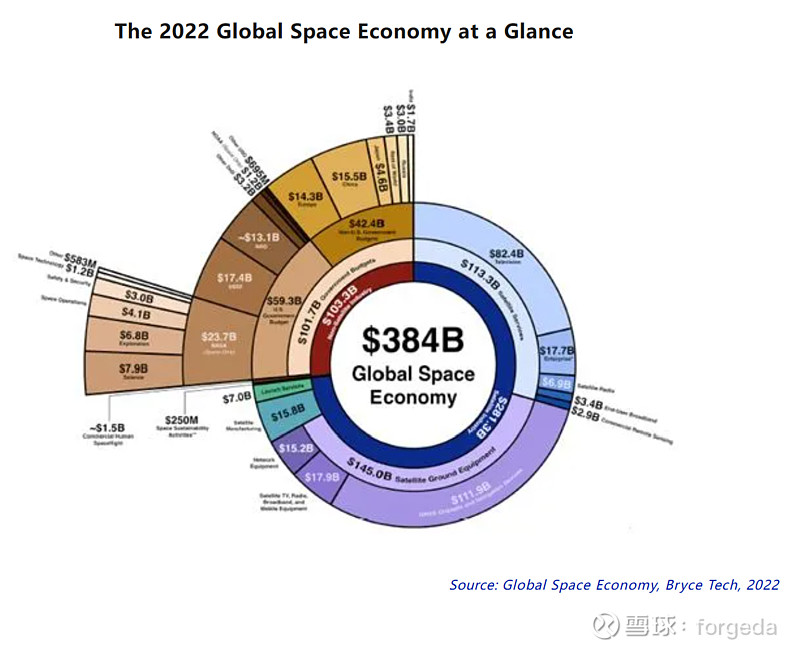

到2022年时,全球太空经济的规模已达3840亿美元,近28000亿人民币。

芯片行业往往是老大吃肉,老二喝汤,其它的都像是被扔进斗兽场,与追逐高风险高回报的新药研发行业较为类似。

FPGA芯片,以及建立在其算力基础上的EDA硬件辅助验证,在技术底层、商业模式等方面,尚未发生范式转换。在可预见的较长时间内,更多是群雄逐鹿,而非像其它科技行业类似“寡头共治”。

以至于电子工程专辑(EE times)在回顾2009年以前,为什么有那么多FPGA初创企业会倒下,原因之一是"生于产品最小可行性验证MVP,没于产品和市场适配PMF":

这些芯片厂商“低估了”研发专用EDA软件的难度!

如果要找一个对FPGA功能安全需求,与空间应用最接近的行业作为平替备选的话,汽车电子无疑将排名居前。

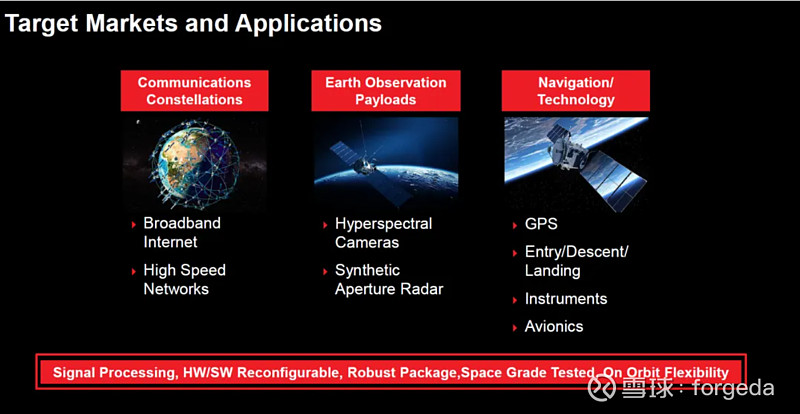

FPGA市场营收排名第三,芯片出货量最大的$莱迪思半导体(LSCC)$,2022年宣布进军航天市场。

目标是商业航天,特别是低轨卫星的数据处理。

选择的合作伙伴也大有来头,前身是英国第三大防务公司Cobham的先进航天电子部门CAES,其航天器件可靠性业务,几乎参与了欧美所有重要的航天工程。

包括1969年阿波罗11号以来的每一次载人航天任务。

2023年被PE资本收购后,以FrontGrade品牌开展业务。

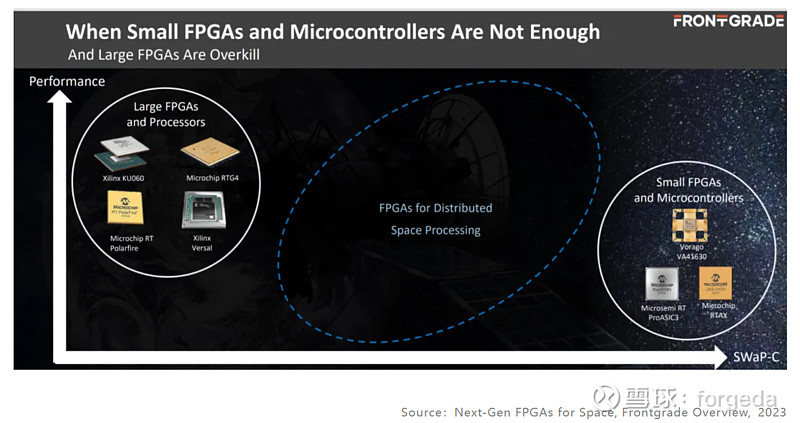

将莱迪思中小规模FPGA在空间市场的机遇定位为,目前市场上两强的大芯片,要么过“大”,显得“浪费”;小芯片的性能,又太拉垮。

从用户成本角度,先进的大容量耐辐射芯片,一片售价可高达20万美元;

而小规模的抗辐FPGA和CPU芯片,通信带宽和处理能力都有限,只能执行简单的功能,无法作为卫星处理的"大脑"。

除了性能因素,以及对面积(Size)、重量(Weight)、功耗(Power)和成本(Cost),即SWaP-C的权衡,对AI处理的支持也必不可少。

只有那些“不大不小刚刚好”FPGA,才正合适。

FrontGrade的股东,Veritas资本不显山露水。

作为全球最大的政府服务基金,目前管理400亿美元资产,主要投资于那些为政府和商业客户提供关键产品、软件和服务的科技公司。

虽然不为大众熟知,但从2012年以来,已经实现20倍的增长。

在大多数投资机构认为很难接受和融入、认为“难搞”的政府环境,深耕数十年。即便经历了互联网、移动互联网时代的投资繁荣期,始终未被诱惑,越出投资边界。

其创始人也被高盛CEO称为“低调,靠实干产生了巨大的影响力”。

这至少已经是Veritas资本涉及的第二家与FPGA业务相关的公司了。

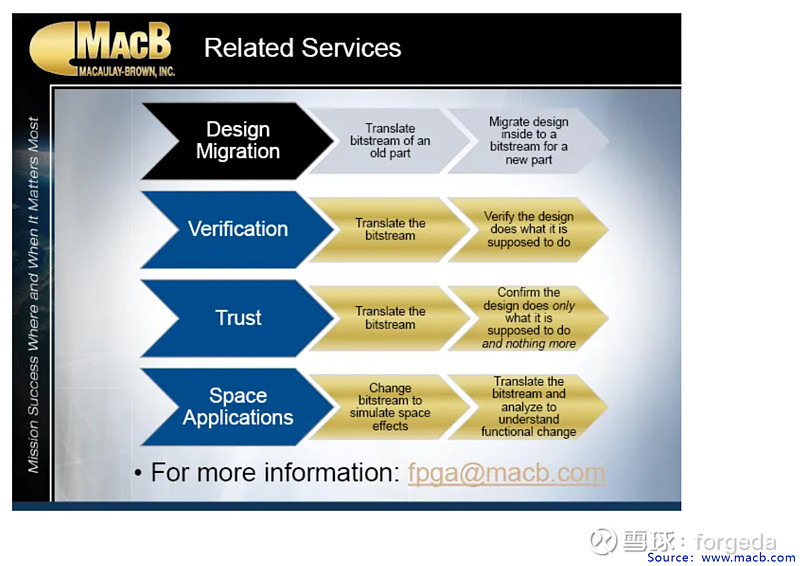

2015年时,收购拥有航天与防务、以及政府业务的Alion公司。三年后,又以该公司为主体,收购MacB公司。

后者聚焦政府和防务领域信息安全,也是美国“可信微电子计划”的主要参与者之一。

MacB公司在庆祝成立35周年时,将其拥有的FPGA位流安全解决方案,拔高到“美国未来十年、甚至更长时间都迫切需要的独特产品和创新解决方案”。

其中也包括航天领域单粒子效应的测试验证。

与MacB公司的位流分析工具,在空间应用服务,占比较小不同。

莱迪思也成为继赛灵思、Microsemi两大厂商之后,FrontGrade合作的第三家FPGA大厂。

软件和EDA巨头新思合作,硬件有行业元老加持,谋定而后动,对空间市场前景,抱以厚望。

从芯片厂商的视角,在器件架构、制造工艺上进行加固,在FPGA的整个应用生命周期中,只是起点。

用户使用EDA开发软件,在硬件设计上通过多模冗余以及抗辐加固手段,如ECC、CRC等,以尽可能实现预期的可靠性和可用性需求,更多着力在设计流程。

但在终端用户设计开发层面,对于包括莱迪思在内的新进入者来说,至少从赛灵思已有的成功实践看,可能还不够。

人们用FPGA实现的创新大张旗鼓,但往往对里面使用的芯片秘而不宣。

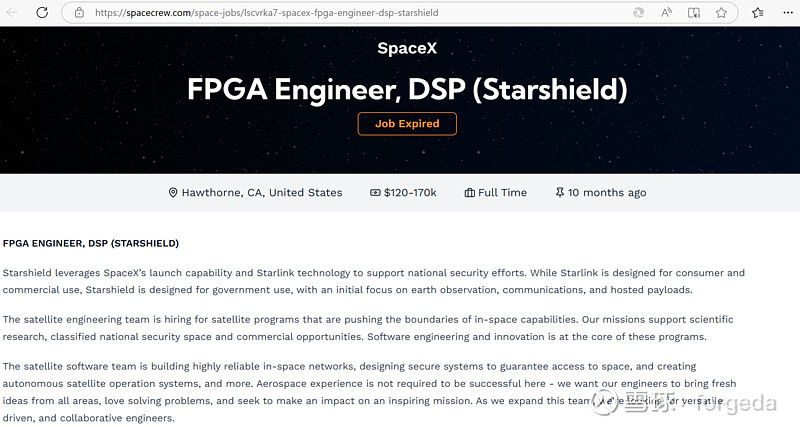

号称对专利最为开放的马斯克,旗下Starlink卫星中的星载FPGA平台,网上公开的信息寥寥,更趋封闭保守之势。

据说在赛灵思芯片应用开发过程中,调试验证方面就曾遇到大麻烦。按照好事者不经意的爆料,“ZU19EG就卡在了SEL指标的重离子测试环节没有放行,具体细节无可奉告。”

开发周期长,应用编程难度大,不是说说而已,全世界用户都感同身受。

那就只能是常年招人了。

虽然早在2018年,Starlink就将用赛灵思ZU9EG实现的实时低轨星座制导系统,以及抗辐射加固设计等“疑难杂症”,就已经外包给JPL解决,并由后者提供技术服务和工程支持等贴身服务。

但其系列公司在官网,以及其他招聘平台,也是常年发布旗下"航天全家桶"所需的FPGA应用设计工程师、IC验证工程师招聘广告,长期有效。

按照赛灵思公司从1998年以来在航天领域的服务路径,即便芯片在器件层面可靠性只是差强人意,但如果能够在短时间内修复,仍可能达到预期设计目标。

商业航天作为战略性新兴产业,2023年首进中央经济会议,在政策导向资本的现在,可以预期其在国内发展,将得以加速。

空间高性能计算时代的黎明

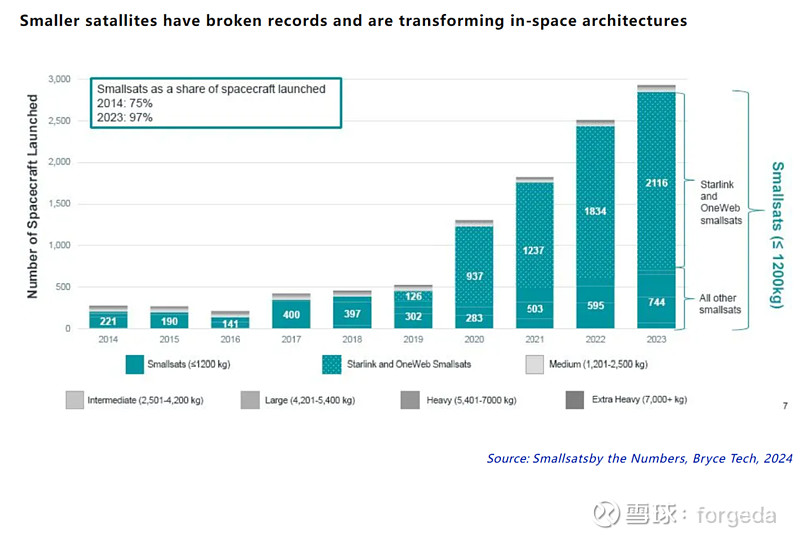

以商业卫星为例,包括低轨卫星组群概念等,为整个FPGA应用市场注入全新的增长动力。

如果没有器件层面的低成本和高效能,将是很难想象的事情。全球在轨小卫星迭创新高,数量不断创纪录,正在重塑太空架构。

2014年,数量是221颗;2023年时,多达2860颗,成为绝对主角。

国内预计部署的卫星数目,据不完全的粗略统计,将是破纪录的6万颗左右。

不管是Starlink低至千万级别以内造价的商业卫星,还是券商调研报告所称的国内单星成本为4500-6500万/颗,其中卫星载荷的转发器/天线分系统使用的FPGA部件,约200万元左右。

即便排除数据处理性能和供应商产能等因素,可能还买不到几颗类似微芯科技的高等级芯片(anti-fuse FPGA),仅此一项成本,就足够不现实。

或许正像科技纵览杂志(IEEE Spectrum)在评论航天电子未来发展趋势所说的,过去我们认为理所当然的一切,比如做事的方法,可接受的理念,以及最佳实践等,现在都受到了质疑。

“Everything we used to take for granted about how you do something, what's accepted, best practices - everything's been questioned”

$航宇微(SZ300053)$ 二十年前发布国内首款基于SparcV8架构的抗辐照CPU芯片,激起浪花朵朵。

按照欧比特董秘和股民交流回复,其2021年采用ARM架构研制的人工智能处理器芯片,主要面向智能安防、机器人和智能制造等应用领域。2023年初,进入封装阶段。

珠海国资背景的创投公司,也是相当生猛,2023年同时投资了錾芯半导体和中科芯磁,两家珠海的FPGA初创企业。

$微芯科技(MCHP)$ 接手NASA HPSC项目,金额5000万美元,约3.65亿人民币,内嵌处理器架构也从ARM,转向更为开放便宜的RISC-V。

如果要找一个对FPGA功能安全需求,与空间应用最接近的行业作为平替备选的话,汽车电子无疑将排名居前。

进入到智能汽车时代,后者作为众多FPGA厂商的芯战场。

那么在商业航天快速推进的今天,空间会成为应许之地吗?

或许就像赛灵思早年所说的那样,不管是用于日常调试,还是安全验证等高级应用,您所需要的,仅是一款合适的工具。

告别芯片硬件底层细节的痛苦,在硬件加速一切的异构计算时代,加速取得成功。

Make Money

能够更多专注于与众不同的核心竞争力。

缩短产品开发周期,并为最终产品注入更多信心。

时间是优秀企业的好朋友,时间成本同时也是企业的最大成本。

省钱即赚钱。

Save Money

用EDA工具的自动化算力,扩展工程师的能力。

无需打破用户现有熟悉的设计流程,把脏活累活,繁琐重复的体力活,都交给工具代为完成。

把工程师觉得门槛低,容易做的快速完成。

以人为本,工具为辅。

复杂的疑难问题,辅助完成,可帮助工程师更好地释放创新能力。

加速设计左移,提升设计生产力。

仅就工具本身对用户的价值而言,特别是第三方的EDA软件,也应当告别复杂且昂贵的专用设备、高级解决方案,需要长时间学习培训才能使用的专家系统。

终极的复杂,是简单。

就像新加坡联合早报网《重建网络巴别塔》一文中所描述的:“这几天打开小红书,让人想起千禧年前后刚接触互联网时的新鲜感,近30年来,头一次遇到。

过去更多的交流机会局限在受过高等教育、拥有先进资源的精英阶层,如今则是连完全不会说对方语言的普通人都能无缝沟通。

与当年不同的是,即时翻译软件的发展与普及,使得跨语言沟通门槛大幅降低。如果说此前少数人架起梯子,转述外边发生的事,现在则是网民冲开一道口子,让两边的人直接看到对面的风景。

抖音、快手和微博等中国社媒平台,有些只能在中国区应用商店下载,有些要提供中国手机号才能注册。而小红书可以直接在美区应用商店下载,也不需要实名验证,直接被冲上排行榜第一”。

网络连接一切,硬件加速一切。

我们身处技术普惠、算力平权、点石成金的创新变革时代。

变化正在发生,一切皆有可能!

全文完,感谢您的耐心阅读

::参考资料::

[1] SpaceX: 在座的各位,都是垃圾! 创业邦,2024

[2] FPGA Verification Accelerator. NASA, MAPLD 2008.

[3] Paul Schumacher, SEU Emulation Environment. Xilinx,2012

[4] ESA strategy ASIC & FPGA for space. ESA, 2013

[5] Spatial Debug & Debug without re-programming. MicroSemi, 2016

[6] Hidalgo, Verification Strategy of Multi-FPGA Systems. Airbus Crisa,2023

[7] 芯片的征途不止于星辰大海. 新思科技,2023

[8] 陈婧:重建网络巴别塔. 联合早报,2025

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)