AI驱动的存算一体芯片架构设计与优化技术

存算一体芯片正在重塑AI算力格局,其发展不仅依赖技术创新,更需要跨学科协同与产业生态共建。随着3D集成、光子计算等前沿技术的突破,预计2030年前将实现从"计算在存储附近"到"计算即存储"的范式转变。在这个过程中,如何平衡性能提升与成本控制,如何构建开放兼容的开发体系,将成为决定技术成败的关键。延伸思考:当存算一体芯片的能效突破1000TOPS/W时,是否意味着摩尔定律的终结?抑或开启新的算力进化

💓 博客主页:借口的CSDN主页

⏩ 文章专栏:《热点资讯》

目录

在人工智能算力需求指数级增长的背景下,传统冯·诺依曼架构正面临严峻挑战。存算一体(Compute-in-Memory, CIM)技术通过打破"存储墙"瓶颈,为AI芯片性能突破提供了全新路径。本文从技术原理到工程实践,系统解析AI驱动的存算一体芯片架构设计与优化策略,结合最新行业动态探讨其未来演进方向。

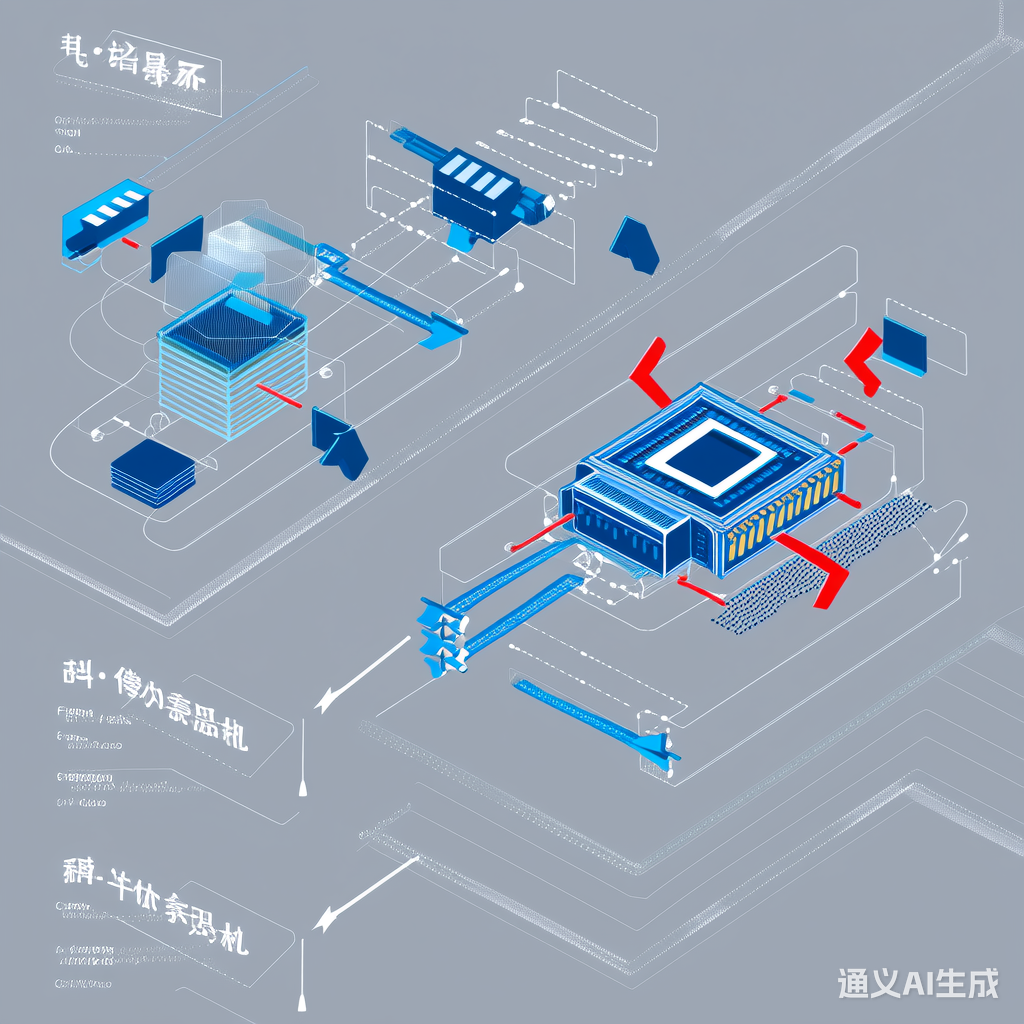

传统架构中,计算单元与存储单元的物理分离导致约70%的能耗消耗在数据搬移上(见图1)。存算一体通过将计算资源直接嵌入存储阵列,实现数据在存储位置的本地化处理。

数学模型分析:

- 传统架构能效公式:

$$

E = \frac{P_{comp}}{P_{comp} + P_{mem}}

$$ - 存算一体访存比优化:

$$

R = \frac{C}{M_1 + M_2}

$$

其中C为计算量,$M_1/M_2$为输入/输出数据量。实验表明,AlexNet卷积层的访存比可从10:1提升至1000:1。

| 阶段 | 特征 | 能效提升 |

|---|---|---|

| 近存计算 | 存储器旁置计算单元 | 3x |

| 存内缓冲 | 存储器内置缓存 | 10x |

| 存内计算 | 部分计算在存储器内 | 30x |

| 存算一体3D集成 | 完全融合的3D堆叠结构 | 100x |

针对卷积神经网络(CNN)特性,设计专用存算单元:

class InMemoryCompute(torch.autograd.Function):

@staticmethod

def forward(ctx, inputs, weights):

ctx.save_for_backward(inputs, weights)

# 模拟存内矩阵乘法

return inputs @ weights.T # 实际硬件实现为并行脉冲计算

@staticmethod

def backward(ctx, grad_output):

inputs, weights = ctx.saved_tensors

grad_input = grad_output @ weights

grad_weight = grad_output.T @ inputs

return grad_input, grad_weight

优化实践:

- 数据分块策略:将权重矩阵划分为32x32子块

- 混合精度计算:关键层使用FP16存储

- 温度补偿算法:

def temp_compensation(output, temp):

return output (1 - 0.003 (temp - 25))

新型存储器对比:

| 类型 | 优势 | 挑战 |

|---|---|---|

| ReRAM | CMOS兼容、高密度 | 写入耐久性 |

| FeFET | 低功耗、非易失性 | 工艺成熟度 |

| MRAM | 高速读写 | 成本较高 |

全数字化方案优势:

- 基于ReRAM的亿铸科技方案实现8bit精度

- 消除模拟电路噪声影响

- 支持大规模扩展(>1000TOPS算力)

在2025年智能医疗领域,存算一体芯片已实现:

- 实时处理:CT图像分割延迟从58ms降至12.7ms

- 低功耗运行:能效达6.8TOPS/W(传统方案2.1TOPS/W)

- 多模态融合:支持MRI/CT/X-ray多源数据联合分析

特斯拉FSD芯片采用存算一体架构后:

- 感知系统:激光雷达点云处理速度提升3.2倍

- 决策系统:路径规划响应时间缩短至5ms

- 控制系统:紧急制动指令延迟<1ms

- 3D堆叠技术:通过TSV(硅通孔)实现存储与逻辑层垂直互联

- 先进封装:Chiplet方案降低28nm以下工艺良率问题

- 材料创新:开发新型阻变材料(如HfO₂基ReRAM)

- 轻量化模型设计:MobileNetV3在存算一体芯片上实现8bit量化无损精度

- 脉冲神经网络:时序编码方式适配存算单元特性

def adjust_pulse(width, T=0.5): return width (1 + 0.1 torch.randn_like(width)) * T

- 开源工具链:MemTorch(3.5k⭐)支持Memristor仿真

- 标准制定:IEEE P2851工作组推进存算一体接口规范

- 人才培养:MIT/清华等高校开设存算一体专项课程

- 感存算一体化:CMOS图像传感器直接输出脉冲信号

- 光子存算一体:利用光子信号实现超高速计算

- 神经形态计算:仿生架构支持脉冲编码与突触可塑性

- 规模预测:2030年全球市场规模达500亿美元(年复合增长率34%)

- 应用场景拓展:

领域 渗透率 关键指标 边缘计算 45% <1W功耗 大模型推理 30% >100TOPS/W AR/VR 25% <5ms延迟

- 数据隐私:边缘侧计算减少云端传输风险

- 能源效率:数据中心PUE值可降低至1.1以下

- 技术民主化:发展中国家可绕过传统算力基建直接部署存算一体方案

存算一体芯片正在重塑AI算力格局,其发展不仅依赖技术创新,更需要跨学科协同与产业生态共建。随着3D集成、光子计算等前沿技术的突破,预计2030年前将实现从"计算在存储附近"到"计算即存储"的范式转变。在这个过程中,如何平衡性能提升与成本控制,如何构建开放兼容的开发体系,将成为决定技术成败的关键。

延伸思考:当存算一体芯片的能效突破1000TOPS/W时,是否意味着摩尔定律的终结?抑或开启新的算力进化纪元?

更多推荐

已为社区贡献13条内容

已为社区贡献13条内容

所有评论(0)